公司簡介

現有發明專利 16 項, 包含台灣, 美國, 日本, 大陸,...

公司沿革

2007年:

7月正式成立,公司定位於IC設計公司。

「槽式功率金氧半電晶體及其製作方法」向台灣、大陸、美國提出發明專利申請。

2008年:

加值型之槽式功率金氧半電晶體結構向台灣、大陸、美國、日本提出發明專利申請。

產品結構特性驗證完成。

2009年:

「槽式功率金氧半電晶體及其製作方法」(I) (II)之台灣、大陸、美國專利,公告。

獲得中華民國經濟部 SBIR 科技研究發展專案經費補助。

完成 20V P-MOS 驗證

2010年:

獲得美國專利 TRENCH-TYPE POWER MOS TRANSISTOR AND INTEGRATED CIRCUIT UTILIZING THE SAME。

完成 30V P-MOS, 20V N-MOS 驗證

2011年:

完成開發全球第一顆多合一 Power MOSFET。

完成全球第一顆 WLCSP 封裝 pPower MOSFET.

2012年:

產品量產 – PT4953E3, PT4953E6, PT9435E3, PT9435E6, PT3401, PT3407, PT9926A, PT9926B, PT8205,PT2301, PT2302, PT2303。

完成 40V ~ 60V N-MOS P-MOS 驗證

完成 80V N-MOS 驗證

產品服務

Product Line,

1. Power MOSFET [PTMOS]

2. Analog IC

全球首創技術

Multi Power MOSFET Single Chip

PT-MOSFET

Power MOSFET with Control Circuit Single Chip, CMOS Compatible

None epi-wafer Power MOSFET

None Backside-Metal Power MOSFET

Power MOSFET MP by 12” Wafer Technology

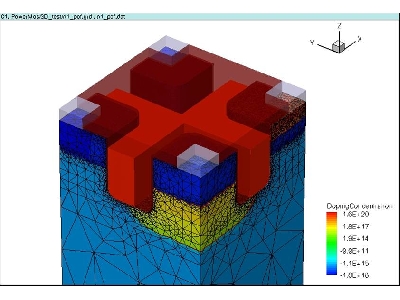

本公司開發「新一代高效能Power MOSFET製程技術」,將以全新的結構設計,提供Power MOSFET更佳的可靠度,及大幅減少製造成本為目標。本案技術中採用平面式結構(Planner Trench Field Drift MOSFET,簡稱PT MOS)設計,不同於UMOS的垂直結構,其結構適用一般晶圓材料製作及高密度設計之應用並相容一般CMOS的製程,因此,在晶圓方面,只要採用價格為Epi-Wafer 1/3的一般Wafer即可達成,且無需傳統製程的Backside Metal,而且,所生產之功率晶體的大小僅為傳統技術的1/3,由於尺寸縮小,若以8吋晶圓估算,其產能可提高3倍以上,綜上優點,本案技術可讓Die的製造成本減少近70%,若再加上技術授權金,可降低之成本相當可觀。

更重要的是本公司已掌握開發本案之專利技術(台灣、大陸發明專利公告中,日本專利申請中,美國第一個發明專利已於2010年取得),具備技術優勢。台灣身為全球IC生產重鎮,未來本案開發完成,可取代現有的UMOS技術,不僅可協助國內電子產品業者減少大幅原料成本、生產成本,更可節省每年龐大的技術授權費用,相當有助於提升國內電子產品產業之競爭力,並且強化國內半導體智財權之優勢。

員工福利

福利說明

◆獎金福利

1.年節獎金

2.分紅入股

◆休假福利

1.週休二日

◆保險

1.勞保

2.健保

◆交通福利

1.停車補助